摘 要:陶瓷基板微系统 T/R 组件具有体积小、密度高、轻量化等特点,正在逐步取代传统微组装砖式 T/R 组件。在微系统封装新技术路线的引领下,T/R 组件对于微焊接技术的需求发生了较大变化。针对基于陶瓷基板微系统 T/R 组件的微电子焊接技术展开了论述,重点阐述了新技术路线与传统技术路线对于技术需求的差异,对围框钎焊、焊球 / 焊柱钎焊、基板与器件钎焊、高密度键合及盖板气密封焊等关键技术进行了介绍,归纳并总结了近年来相关技术领域的研究现状,并给出了现有技术水平条件下满足高可靠、低成本封装需求的最优工艺方法,为微电子焊接技术的发展提供了参考。

随着相控阵雷达技术的发展,特别是微系统封装技术的进步、机电热一体化设计能力的提升及低成本封装JK的引入[1-2],微系统封装设计的T/R 组件正在逐步@代传统砖式微组装T/R 组件,迅速成为行业的研究重点。微系统T/R 组件可满足新一代相控阵天线低剖面、高密度、轻量化的技术需求[3-5],{线单位面积内的组件密度相较以往增加了10~100 M,数量的成M增加使得T/R 组件的成本在整个雷达成本中的占比进一步提升。因此,研究微系统T/R 组件中核心的微电子焊接技术,研究如何提高焊接工艺质量与可靠性并有效降低成本,将直接影响着新一代相控!雷达技术的发展与应用。

当前,微系统T/R 组件虽然经历了数代发展,考虑到其可靠性、使用成本等多方面因素,目前其封装仍然以基于陶瓷基板的T/R 组件三维封装为主,其需要的微电子焊接封装技术主要包括围框钎焊技术、焊球/焊柱钎焊技术、基板与器件钎焊技术、高密度键合技术及盖板气密封焊技术等。目前国内外已发表的相关文献集中在对上述单点技术进行研究或概述[6-15],鲜有文献针对微系统T/R 组件的微电子焊接技术需求展开整体论述。

本文针对基于陶瓷基板的微系统 T/R 组件,对其封装和焊接技术需求进行归纳与分析,梳理了相关焊接技术的研究现状,总结并指出实现高可靠、低成本焊接封装的关键技术,为微电子焊接技术的发展提供了一定的技术参考。

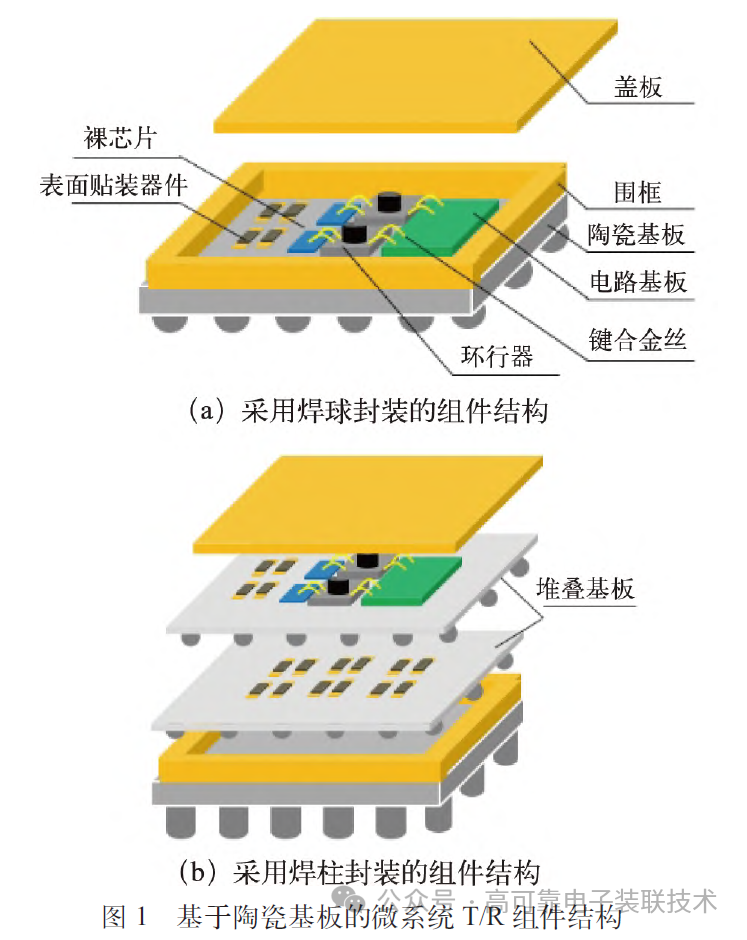

基于陶瓷基板的微系统T/R组件结构如图1 所示,其中陶瓷基板材料常选取低温共烧陶瓷或高温共烧陶瓷,陶瓷基板底部焊点多采用焊球/焊柱,组件内部既有平面微组装也有基板三维堆叠等。T/R组件因其封装集成度高,难以完全避免等器件的失效,少量的组件在经历环境试验后需要对其进行拆盖返修,因此多采用可二次封焊的可伐围框与铁镍合金盖板进行封装。在现有技术条件下,微波器件常用的钛合金、铝硅等轻量化外壳暂不适用于基于陶瓷基板的微系统T/R组件封装。

在基于陶瓷基板的微系统 T/R 组件中,主要应用的微电子焊接技术有:1)将围框封装在陶瓷基板上的钎焊技术;2)在陶瓷基板上植球/ 植柱的回流焊技术;3)针对 T/R 组件内部的电路基板、环行器、表贴器件、堆叠基板等位置的回流焊技术;4)为解决 T/R 组件空间有限问题引入的高密度引线)盖板与围框之间的封焊技术。

本文将重点阐述上述 5 个应用于微系统 T/R 组件的微电子焊接关键技术,分析新技术路线下T/R 组件与传统平面微组装 T/R 组件对技术需求的差异,并结合具体结构进行k入分析,给出现阶段满足高可靠封装需求的最优工艺方法,进一步指导微系统 T/R 组件的低成本封装工艺设计。

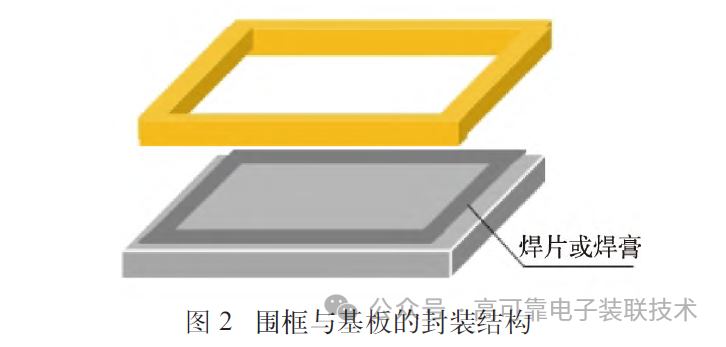

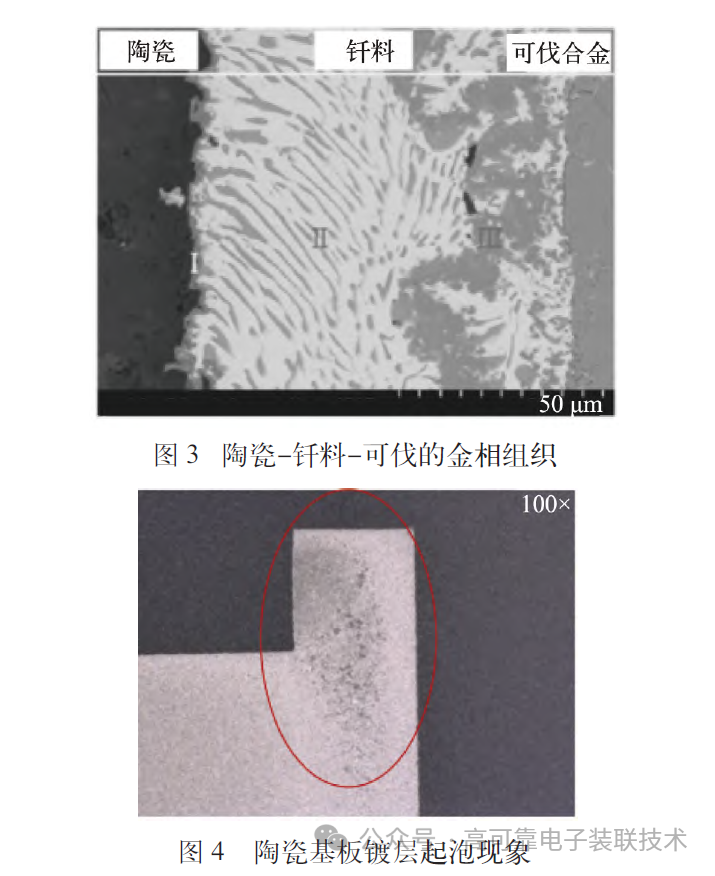

基于陶瓷基板的微系统T/R 组件,其围框多采用可伐JK,围框与基板的封装结构如图2 所示。为了D开S度梯度,业内普a对可伐围框与基板的焊接面进行镀Ni 处理。采用W性的Ag-Cu(-Ti)钎K对陶瓷/可伐接头进行Q空2钎焊,其最低接头强度R为30MPa,最高强度为144 MPa,陶瓷-钎K-可伐的金相组织如图3 所示,钎焊接头的界面组织6匀一致,其气密检测可以实现小于1×10-8Pa·m3/s的漏率。部分从业人员在可伐围框与基板的焊接面镀Ni/Au,采用Au-Ge、Au-Ga、Au-Si、Au-Ag-Si、Au-Sn、Pb90-Sn 等A钎K对其进行Q空A钎焊(N晶炉,无助焊剂)或Q空回流焊(有助焊剂)[23-24]。

由于Ag 基2钎K、Au 基A钎K的价格过于昂贵,应用于气密封装场合会增加T/R 组件的成本。同时,由于常S已经达到了A钎K再结晶S度Tr [Tr=(0.45~0.6) Tm,Tm 为固相线],且钎焊密封面与外界环T直接接‘,非N晶成分A钎K(如Pb-Sn 等)的钎焊面相对更容P蠕变失效及在钎焊界面形成:柯肯达尔空洞,导致在后续加严环T试验考核中P出现气密失效的现W,因此除在z空z{、R工电子芯片封u等应用场合(选择使用Ag 基或Au 基钎K外,类似需要使用金属围框钎焊的场合建议优选Cu-Sn-Ti 合金钎K[29-30],其接头强度R为42 MPa,钎透率与气密性6满足使用需求。使用Cu-Sn-Ti 合金钎K3能大幅降低JK成本(以实时价格计算,价格R为Ag 基钎K的1/50、Au 基钎K的1/4 500),又能有效规避非共晶成分软钎料蠕变失效的风险。

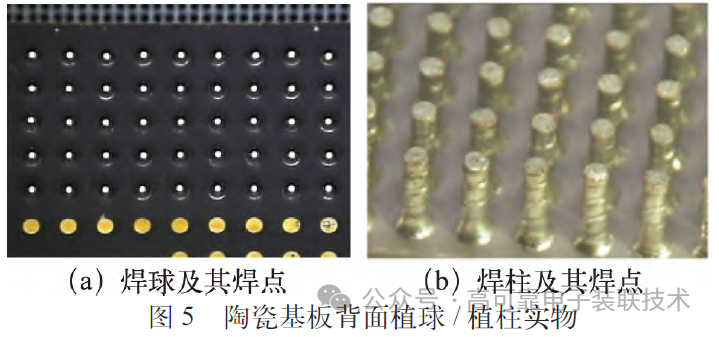

在陶瓷基板的底部需使用焊球/焊柱将信号输入/输出,考虑板级表面组装技术(SMT)整体工艺及拉开温度梯度的需求,须预留一个低温钎焊窗口。从封装可靠性角度出发,目前植球/ 植柱普遍采用熔点为183℃的Sn63Pb37钎料。根据IPC-7095D标准及美军标相关要求,采用焊球封装的高可靠T/R 组件的尺寸一般需小于15 mm×15 mm,采用焊柱封装的高可靠T/R 组件的尺寸需小于52.5 mm×52.5 mm,且由于陶瓷基板与电装电路板之间存在热失配,为了进一步提高焊球/焊柱的使用寿命,推荐采用金属基(如Cu)增强的材料[31]。陶瓷基板背面植球/植柱实物如图5所示。

由于微系统T/R 组件对控制重量有较高要求,目前除铜丝缠绕焊柱外,其他的金属基增强焊球/焊柱因为本身易超重,其在T/R 组件中的推广应用仍然受限。为了缓释陶瓷基板与电装基板之间的应力,减少因边角翘曲造成的焊点失效,一方面需严格按标准规定的尺寸限制T/R 组件的尺寸;另一方面需对焊球采用底部填充胶粘、边角绑定胶粘等加固工艺[32-33]。根据梅聪等[34]的研究结果,在-55~125 ℃的试验条件下,有底部填充保护的焊球的焊点寿命约为1 350 个循环,比无底部填充保护的焊球的焊点寿命提升了2倍。针对焊柱也扩展出了铜丝缠绕叠加局部底部填充胶粘的双重加固抗应力工艺[35],可以将残余应力减少70%以上,提升焊点的可靠性。

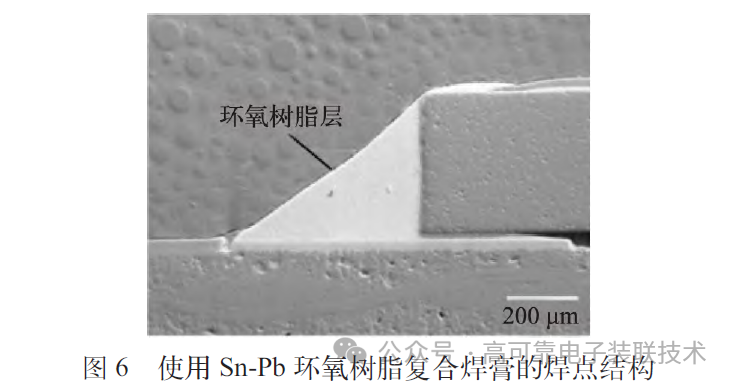

依赖胶填充的工艺方式会使得被胶填充的封装面无法进行返修,行业工作者已关注到焊球/焊柱的焊点返修难的问题并进行了深入研究,研发出一种自防护Sn-Pb环氧树脂复合焊膏[36-37],使用该焊膏的焊点结构如图6所示。采用该环氧树脂复合焊膏的焊点剪切强度为54.51 MPa,比使用传统焊膏的剪切强度高出了36.3%,且经过300次温冲后使用传统焊膏和复合焊膏的焊点剪切强度分别下降了21.2%与13.4%。因复合焊膏的树脂层较薄且仅覆盖在焊点表面,其既能加强焊点的应力防护,同时也方便对封装面进行多次返修。

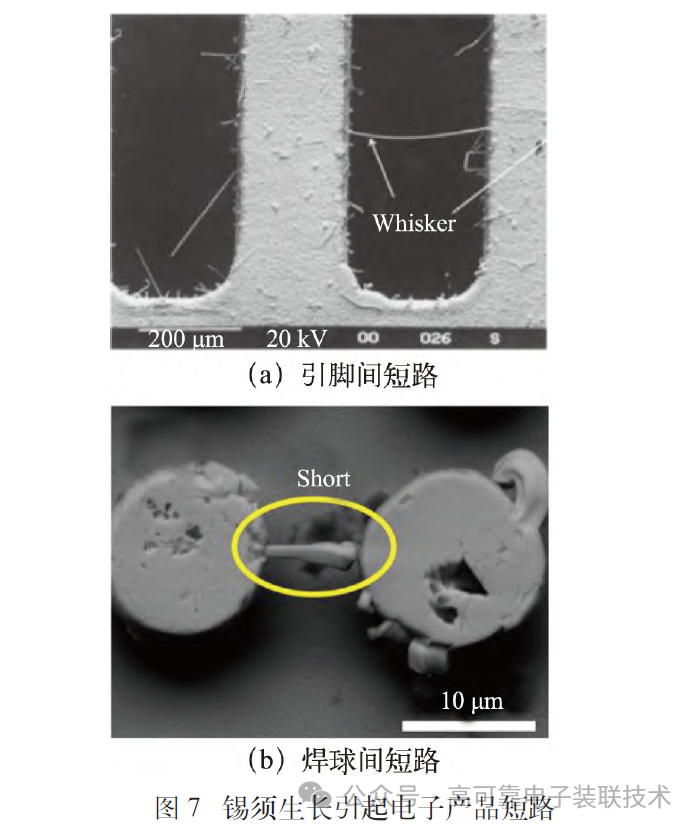

在新技术路线下,由于板级SMT工艺主要使用熔点为183 ℃的Sn63Pb37 钎料,且芯片共晶、环行器微机械加工及围框钎焊等工艺主要使用熔点为280℃的Au80Sn20钎料,导致T/R组件内部的一些元器件、电路基板及环行器的钎焊必须采用熔点为210~250℃的含Pb 钎料(参考NASA 采用的IPC J-STD-001DS标准,补充要求中规定钎料中Pb 的质量分数大于3%)。无铅锡银铜(SAC)钎料与Sn63Pb37钎料的熔点相差30 ℃,可以满足焊接温度要求,但因其极易产生锡须短路,会造成大量电子元器件及精密仪器的损坏,锡须生长引起电子产品短路如图7所示。军用飞机、民航客机以及军/民用卫星等,均有因为锡须短路引发故障的记录。目前关于锡须的生长机制争议较大,普遍认可的有位错机制、再结晶机制、氧化层破裂机制、压应力机制、活性锡原子机制5 种,建议慎重选择尚未完全清楚机理的材料用于T/R 组件等产品的高可靠封装。

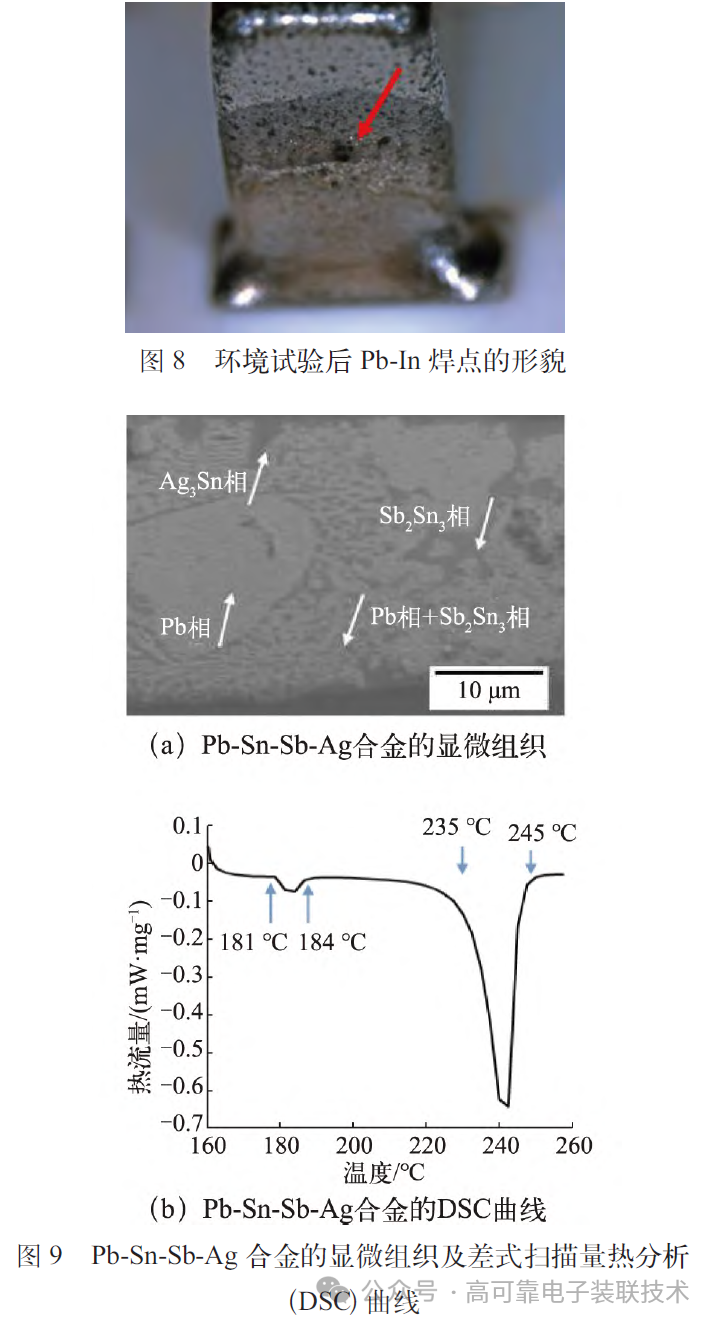

面对软钎料需求的缺口,行业工作者首先尝试使用熔点为210~240 ℃的Pb-In 钎料,其优点是两种元素与Au元素之间均不会反应,没有硬脆的Au基化合物产生,后续无须进行去金处理,缺点是在环境试验过程中In元素会与镀层发生反应,侵蚀过度造成焊接失效,环境试验后Pb-In焊点的形貌如图8所示。环境试验后Pb-In 焊点的剪切强度普遍小于5 MPa,强度较低难以满足使用需求。北京有色金属与稀土应用研究所[44]公开了一种Pb-Sn-Sb-Ag 钎料,其熔点为235~245℃,该钎料的优点是强度高且可设置与LED、汽车等消费电子行业使用的Sn-Sb无铅软钎料通用的回流焊温度,缺点是Pb-Sn-Sb-Ag 合金存在低熔点相[45],Pb-Sn-Sb-Ag 合金的显微组织及差式扫描量热分析(DSC)曲线 所示。低熔点相的存在导致Sn63Pb37钎料在210℃的回流焊温度下发生软化,此时接头强度不大于1 N,导致器件因炉中链条的振动而跌落。本文结合工程实践并联合北京康普锡威科技有限公司与北京有色金属与稀土应用研究所等单位提出了优化合金成分的方法,制备改性的Pb-Sn-Sb-Ag 钎料,消除了低熔点相,实现了Pb-Sn-Sb-Ag钎料的焊点在210 ℃时仍具备足够强度,该新型焊料具备作为微系统封装用软钎料的潜力。

从降低成本的角度出发,除了将改性的Pb-Sn-Sb-Ag合金作为微系统封装用软钎料,另外两个研究方向是张富文等[46]在SAC 钎料中添加抑制锡须生长的元素,以确保钎料在T/R 组件寿命时间内不产生锡须,或者是针对Sn-Pb软钎料进行改性,实现低温焊接高温使用,可在210℃时进行两次回流。

键合是微电子焊接中最为重要的工艺之一,也是T/R 组件封装的关键工序。目前在T/R 组件中仍有90%以上的芯片采用金丝键合技术实现电气互连。在高密度微系统T/R 组件中,芯片键合焊盘的尺寸由100~150 μm 减小至50~70 μm,且由于组件高度的限制,键合弧度需相应变小。采用传统键合工艺的微系统T/R 组。